近日在英特尔马来西亚科技巡展上,英特尔逻辑技术开发副总裁Bill Grimn详细介绍了Intel 4制程工艺。根据IDM 2.0战略,英特尔计划在四年内实现五个制程节点,包括而Intel 4处于计划中的第二个节点,将用于即将到来的Meteor Lake,也就是新一代面向移动平台的酷睿Ultra第1代处理器。

Intel 4将采用了EUV(极紫外)光刻技术,可使用超短波长的光,改善良品率和面积微缩,从而实现高能效,而且可应用EMIB和Foveros封装技术,相比Intel 7可提供翻倍的晶体管密度,也为接下来的Intel 3奠定基础。目前正在开发过程中的Intel 3将带来密度更高的设计库,增加驱动电流的晶体管并降低通孔电阻,其将更多地使用EUV光刻技术。

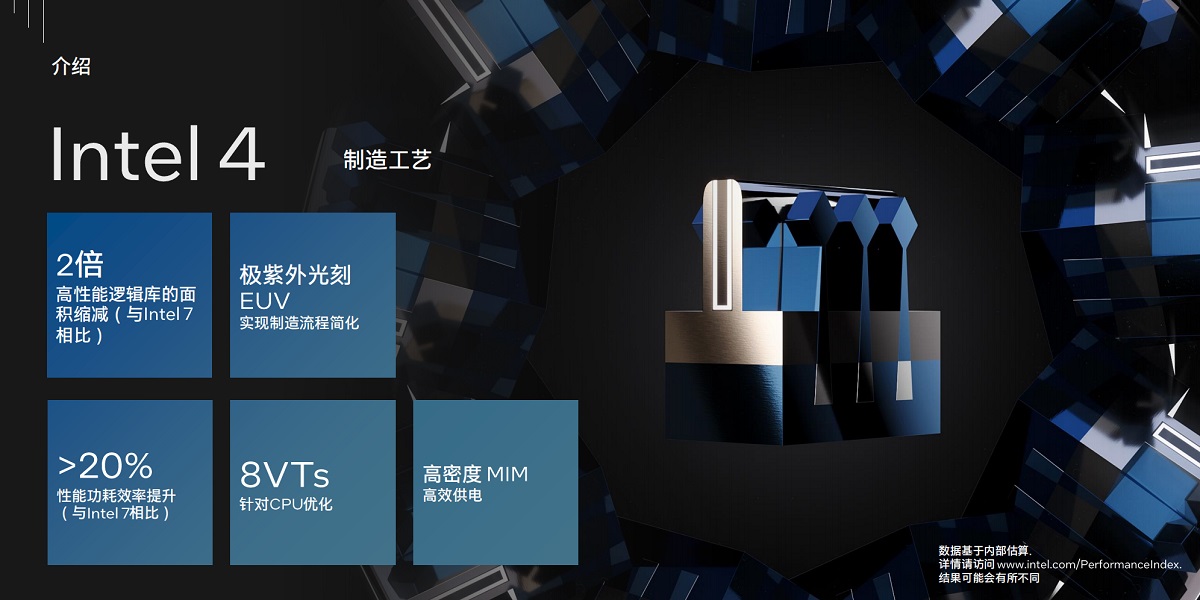

与Intel 7相比,Intel 4实现了两倍的面积微缩,带来了高性能逻辑库,并引入了多个创新,包括引入EUV光刻技术,大幅简化了互连架构的制程工艺,同时还支持微缩,使得Intel 4中的掩码减少了20%,工艺步骤减少了5%;针对高性能计算应用进行了优化,可支持低电压(<0.65V)和高电压(高于1.1V)运行,相比Intel 7,Intel 4的ios功率性能提高了20%以上;另外高密度(金属-绝缘体-金属)电容器实现了卓越的供电性能。

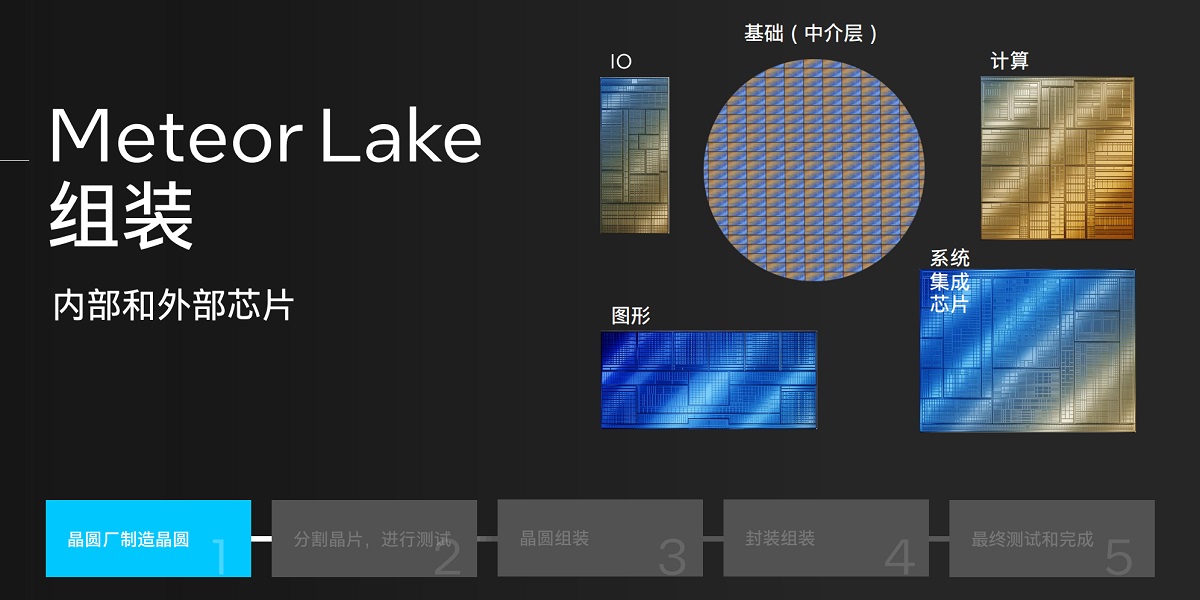

Meteor Lake采用分离式模块架构,由四个独立的模块组成,其中计算模块首次采用Intel 4制程工艺打造,这也是首款内置神经网络处理单元NPU的英特尔处理器。Meteor Lake的独立模块将通过Foveros先进封装技术连接,利用高密度、高带宽、低功耗互连,能够把多种制程工艺制造的诸多模块组合成大型分离式模块架构组成的晶片复合体。

Foveros先进封装具有诸多优势,包括36u凸点间距,迹线宽度小于1微米;凸点密度提高近8倍;迹线长度小于2毫米;160GB/s/mm带宽;功耗小于0.3 pJ/位。相比于Raptor Lake,Meteor Lake通过Foveros先进封装使得低功耗晶片互连最大限度地减少分区开销,同时小区块提高了晶圆良率,初制晶圆更少,而且能够为每个区块选择理想的硅工艺。

据英特尔封装、组装和测试技术开发高级总监Pat Stover介绍,英特尔通过包含五个步骤的工艺组装Meteor Lake:

-

切割 – 从晶圆厂收到内部和外部代工厂的晶圆,并将其切割成单个芯片。

-

分选和测试:单晶片测试确保只有高质量晶片才能进入Foveros组装阶段。这种探测能力是异构设计的关键所在,通过向组装生产线提供更多高质量芯片来提高测试良率。组装生产线已经过主动热控制能力全面测试。

-

晶圆组装 – 在基板晶圆上组装各个模块。该生产线在一个流程中整合了芯片附着、底部填充和晶圆模具等组装操作,以及碰撞、钝化、研磨、抛光等制造操作,这在英特尔尚属首次。

-

封装组装 – Meteor Lake Foveros复合体是在BGA基板面上组装的。这种复合体兼容现有的封装组装工具和工艺,只需进行少许优化。

-

测试和完成 – 最后是英特尔HDMx和系统测试保障质量,包括压力和老化测试、类测试和系统级平台测试。

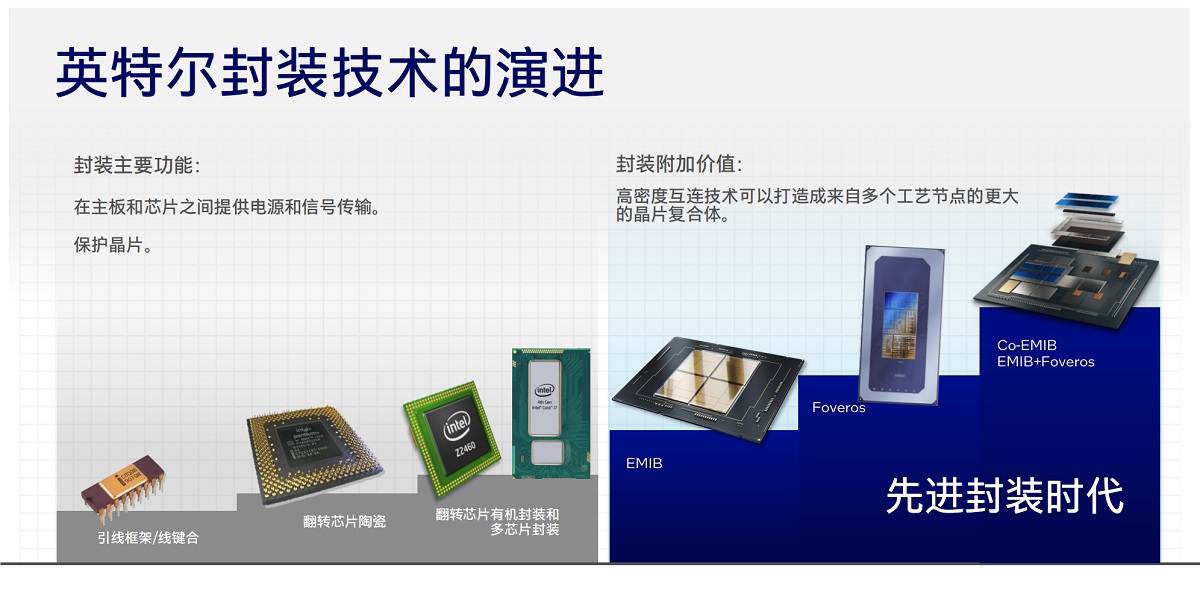

从倒装芯片球栅格阵列(FCBGA)和倒装芯片路栅阵列(F_C_LGA)到嵌入式多芯片互连桥接(EMIB)再到Foveros,最终实现Foveros Direct,英特尔一直走在创新封装技术的前列。此外,英特尔正在进行重大投资,以支持使用晶圆级组装的Meteor Lake及之后的项目,而这些设施将为Foveros Direction 9微米和其他未来项目提供产能。

微信扫一扫

微信扫一扫  支付宝扫一扫

支付宝扫一扫